**Orchestrating a brighter world**

# **HPC Companion** 2019/20 **Technology** Guide

# HPC Companion 2019/20

Technology Guide

# Table of Contents

## Preface

Yuichi Kojima, Managing Director NEC Deutschland GmbH.

# A History of HPC Technology

During the last years NEC x86-systems dominated the HPC-market, with GPUs and many-core-systems recently making their inroads. But this period is coming to an end, and it is again time for a differentiated complementary HPC-targeted system. NEC has developed such a system.

## SX-Aurora TSUBASA

In 2018 NEC has launched the new generation of the SX vector architecture, offering a hitherto unparalleled performance especially for memory-bound applications. This is what the Aurora project is about.

# **NEC HPC Platform**

The last few years have seen a growing interest in Deep Learning techniques, thanks to the major breakthroughs achieved in the fields of computer vision and natural language processing. Complex problems, such as object detection, text translation and speech recognition, can now be solved with relatively small effort leveraging Deep Learning techniques.

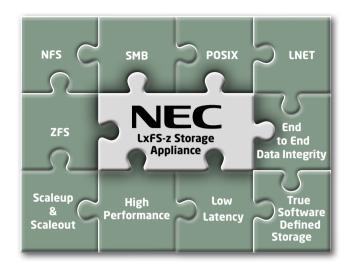

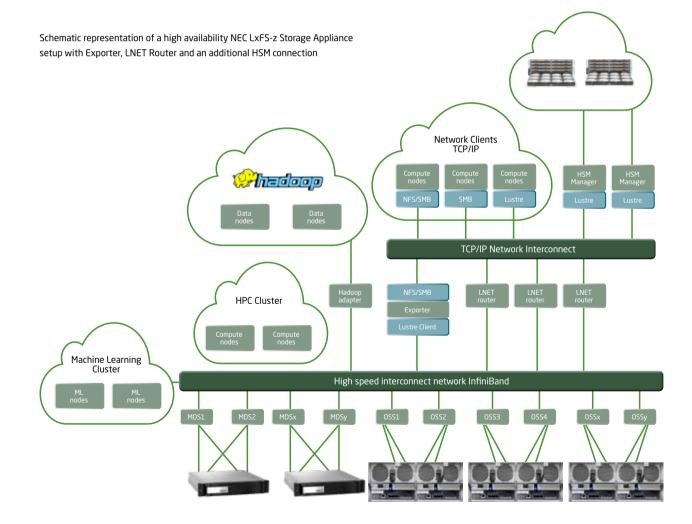

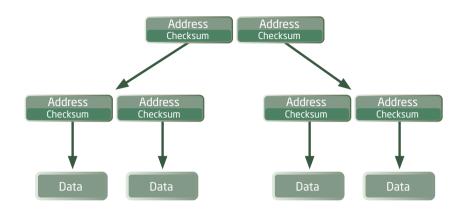

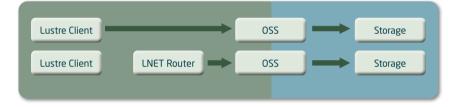

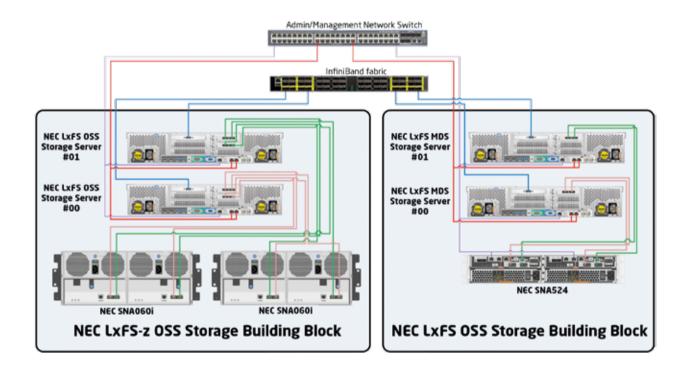

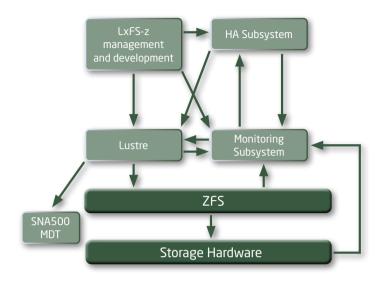

# LxFS-z for HPC Storage

The Lustre file system is a open source, parallel file system that supports the requirements of leadership class HPC and Enterprise environments worldwide.

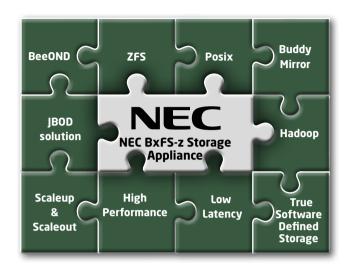

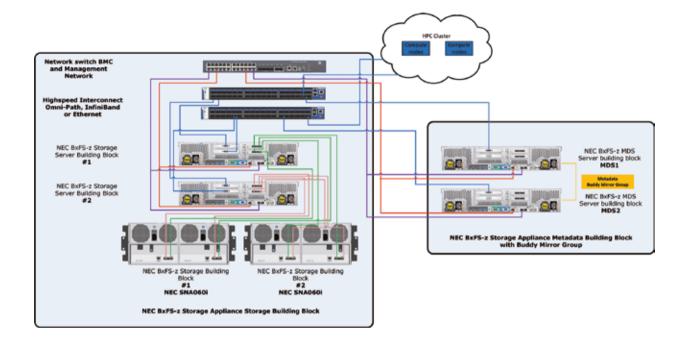

# BxFS-z for HPC Storage

BeeGFS (formerly FhGFS) is the leading parallel cluster file system, developed with a strong focus on performance and designed for very easy installation and management. If I/O intensive workloads are your problem, BeeGFS is the solution.

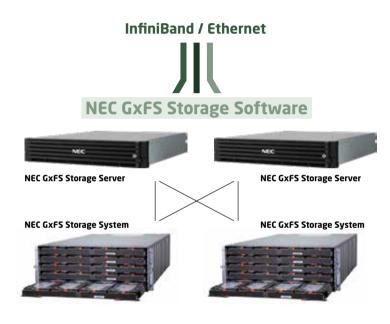

## **GxFS Storage Appliance**

The primary goal of HPC storage is performance: high bandwidth, high IOPS. But the more data are handled, the more important data reliability and enterprise-ready management capabilities become.

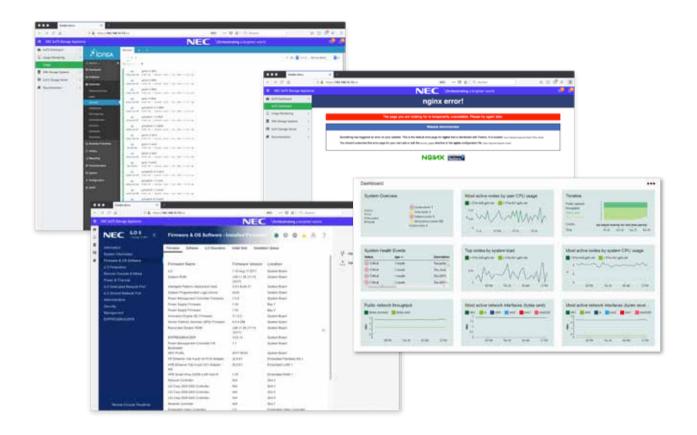

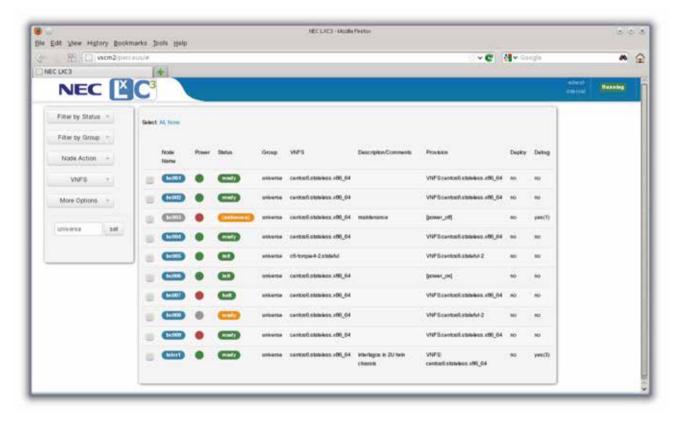

# NEC LXC3-NEO

An HPC system is complex beast. Hiding the complexity underneath a neat and powerful management interface that is easy to handle is most important for both administrators and users. NEC LXC<sup>3</sup> targets this ease of use.

50

16

4

6

#### 74

86

62

#### 108

# NEC as a driver of innovation

Supercomputing and Aritificial Inteligence Made in Japan

High Performance Computing today is many-faceted: it is computational power at its extreme, populating the largest datacenters around the world, utilized for leading-edge research and development by the world's most renowned academic and research facilities. But it has also become mainstream: it is now firmly established itself as the third pillar of science and research alongside theory and experiment.

Artificial intelligence has now experienced a reincarnation, going by the name of "deep learning". Old and well-designed algorithms not only have been improved, but can now deliver to their full strength because the computational capacity provided by the current HPC systems turns their theoretical potential into full predictive power! NEC is a master of HPC, and has been so for decades. We know exactly what our customers from automotive or engineering, medical and life sciences or astrophysical, meteorological and climate research need for optimizing their productive workflow.

But NEC is also a master of Artificial Intelligence. In our Research Labs in Europe, the U.S. and around the world, algorithms are being designed and software is being developed to exploit the full computational power of NEC's vector engine SX-Aurora TSUBASA, designed with highest memory bandwidth and highest sustained application performance in mind.

NEC's solution portfolio for HPC and A.I. comprised not only computational hardware capacity, but also HPC storage solutions based on parallel filesystems commonly used throughout the HPC world. With NEC's deployment solution LXC3-neo, managing a full-fledged HPC environment is made as easy as possible. Our expertise in code and performance optimization, and the excellence of our presales and benchmarking teams is renowned. Our system integration and support team is highly experienced in even the most challenging configurations and a paradigm of customer orientation.

#### Yuichi Kojima

Managing Director NEC Deutschland GmbH Vice President High Performance Computing Europe NEC combines Japanese leading-edge technology with a European spirit. As a comprehensive provider of HPC solutions, we strive after pushing the boundaries of all human achievability, enabling people to live brighter lives. We summarize this approach in our business message: Orchestrating a brighter world.

NEC - HPC Companion 2019/20

# A History of HPC Technology Vector Computing Through the Ages

During the last years x86 systems dominated the HPC market, with GPUs and for some time many-core-systems making their inroads. But this period is coming to an end, and it is again time for a differentiated complementary HPC targeted system.

NEC has now developed such a system based on over 30 years of experience, retaining the virtues of traditional vector systems, in particular high memory bandwidth, combining this with a brand new innovative concept.

This article reviews the past developments of HPC technology, analyzes the status quo, and briefly describes NEC's view on the future and related products.

# **The Early Days**

When did HPC really start? Probably one would think about the time when Seymour Cray developed high-end machines at CDC and then started his own company Cray Research, with the first product being the Cray-1 in 1976. At that time supercomputing was very special, systems were expensive, and access was extremely limited for researchers and students. But the business case was obvious in many fields, scientifically as well as commercially.

These Cray machines were vector computers, initially featuring only one CPU, as parallelization was far from being mainstream, even hardly a matter of research. And code-development was easier than today, a code of 20,000 lines was already considered "complex" at that time, and there were not so many standard codes and algorithms available anyway. For this reason code development could adapt to any kind of architecture to achieve optimal performance.

In 1981 NEC started marketing its first vector supercomputer, the SX-2, a single-CPU-vector-architecture like the Cray-1. The SX-2 was a milestone, it was the first CPU to exceed one GFlops of peak performance. Also Fujitsu and Hitachi were actively pursuing this direction.

# The Attack of the "Killer-Micros"

In the 1990s the situation changed drastically, and what we see today is a direct consequence. The "killer-micros" took over, new parallel, later "massively parallel" systems (MPP) were built based on microprocessor architectures which were predominantly targeted to commercial sectors, or in the case of Intel, AMD or Motorola to PCs, to products which were successfully invading the daily life, partially more than even experts had anticipated. Clearly one could save a lot of cost by using, in the worst case slightly adapting these CPUs for high-end-systems, and by focusing investments on other ingredients, like interconnect technology. At the same time increasingly LINUX was adopted and offered a cheap generally available software platform to allow everybody to use HPC for a reasonable price.

These systems were cheaper because of two reasons: the development of standard CPUs was sponsored by different businesses, and another expensive part, the memory architecture with many CPUs addressing the same flat memory space, was replaced by systems comprised of many distinct so-called nodes, complete systems by themselves, plus some kind of interconnect technology, which could also be taken from standard equipment partially.

The impact on the user was the necessity to code for these "distributed memory systems". Standards for coding evolved, PVM and later MPI, plus some proprietary paradigms. MPI is dominating still today.

In the high-end the special systems were still dominating, because they had architectural advantages and the codes were running with very good efficiency on such systems. Most codes were not parallel at all or at least not well parallelized, let alone on systems with distributed memory. The skills and experiences to generate parallel versions of codes were lacking in those companies selling high-end-machines and also on the customers' side. So it took some time for the MPPs to take over. But it was inevitable, because this situation, sometimes called "democratization of HPC", was positive for both the commercial and the scientific developments. From that time on researchers and students in academia and industry got sufficient access to resources they could not have dreamt of before.

# The x86 Dominance

One could dispute whether the x86 architecture is the most advanced or elegant, undoubtedly it became the dominant one. It was developed for mass markets, this was the strategy, and HPC was a side effect, sponsored by the mass market. This worked successfully and the proportion of x86 LINUX clusters in the Top500-list increased year by year.

Other architectures experienced economical pressure, not only the vector systems, also competing scalar concepts. The HP-precision-architecture is basically gone, MIPS is mostly used for controllers, SPARC is still alive at Oracle and Fujitsu, but it is doubtful that it will recover the development cost. The Motorola-architecture is gone, other microprocessors vanished as well. IBM Power is still alive, but it is at least hard to predict its future. On the vector side Cray stopped the products lines, Fujitsu and Hitachi bailed out, NEC is the only remaining vendor, but committed to the future.

Because of the mass markets it economically made sense to invest a lot into the development of LSI technology. The related progress, which led to more and more transistors on the chips and increasing frequencies, helped HPC applications, which got more, faster and cheaper systems with each generation. Software did not have to adapt a lot between generations, and the software developers rather initially focused on the parallelization for distributed memory, later on new functionalities and features. This worked well for quite some years.

Systems of sufficient size to produce relevant results for typical applications are cheap, and most codes do not really scale to a level of parallelism to use thousands of processes. Some lighthouse projects do, after a lot of development which is not easily affordable, but the average researcher or student is often completely satisfied with something between a few and perhaps a few hundred nodes of a standard LINUX-cluster. Just to put it into perspective, the LINUX-virtual-machine on my Windows laptop is faster than the Cray-X-MP which I used for my thesis.

In the meantime already a typical Intel based dual socket node of a standard cluster has 32 or more cores, this number is still growing. Therefore parallelization is increasingly important. There is "Moore's law", invented by Gordon E. Moore, a co-founder of the Intel Corporation, in 1965. Originally it stated

that the number of transistors in an integrated circuit doubles about every 18 months, leading to an exponential increase. This statement was often misinterpreted that the performance of a CPU would double every 18 months, which is misleading. We observe ever increasing core counts, the transistors are just there, so why not? That applications might not always be able to use these many cores is another question, in principle the potential performance is there.

The "standard benchmark" in the HPC-scene is the so-called HPL, High Performance LINPACK, and the famous Top500 list is based on this. This HPL benchmark is only one, and in fact the latest, of three versions of the original LINPACK-benchmark, this is often forgotten! The other pieces, matrix dimension 100 and 1,000, are rather testing compiler technology and the performance of individual cores, memory latency etc., not scalability, and therefore did not show such a favourable progress in performance. So these small cases could not serve to spawn competition for prestige even between nations.

There are at most a few real codes in the world with similar characteristics as the HPL. In other words: it does not tell a lot. This is a highly political situation and probably quite some money is wasted which would better be invested in brainware.

It is increasingly doubtful that LSI technology will advance at the same pace in the future. The lattice constant of Silicon is 5.43Å. Nowadays typical is a 7nm process. This scale is about 25 times the lattice constant. Some scientists assume there is still room to improve even more, but once the features on the LSI have a thickness of only a few atom layers one cannot get another factor of ten. Sometimes the impact of some future "disruptive technology" is claimed ... there will be ways, there will be limits.

Another obstacle is the cost to build a chip-fab for a new generation of LSI technology. Certainly there are ways to optimize both production and cost, and there will be bright ideas, but with current generations a fab costs at least many billion \$. A slow down of the product innovation cycle, no more tick-tock, is necessary to recover the investment.

## **Memory Bandwidth**

For HPC-applications it is mostly not the compute power of the CPU which counts, it is the speed with which the CPU can exchange data with the memory, the so-called memory bandwidth. If it is neglected the CPUs will wait for data, the performance will decrease. To describe the balance between CPU performance and memory bandwidth one often uses the ratio between operations and the amount of bytes that can be transferred while they are running, the "byte-per-flop-ratio". Traditionally vector machines were always superior in this regard, and this is also one design goal of NEC's new machine. For this reason a vector machine can realize a higher fraction of its theoretical performance on a real application than a scalar machine, the "efficiency".

## **Power Consumption**

One other but really overwhelming problem is the increasing power consumption of systems. A dual-socket-node, depending on how it is equipped with additional features, will consume between 400 Watt and 50 Watt under normal production workload. This only slightly varies between different generations, but seems to increase slowly. Even in Europe sites are talking about electricity budgets in excess of 1 MWatt, even beyond 10 MWatts. One also has to cool the system, which adds something like 10% - 30% to the electricity cost! The cost to run such a system over 5 years will be in the same order of magnitude as the purchase price!

The power consumption will grow with the frequency of the CPU, this is the dominant reason why frequencies are at least stagnating, rather decreasing between product generations. There are more cores, but individual cores of an architecture are getting slower, not faster! This has to be compensated on the application side by increased scalability, which is not always easy to achieve. In the past users easily got a higher performance for almost every application with each new generation, this is no longer the case.

# **Architecture Development**

So the basic facts clearly indicate limitations of the LSI technology, and they are known since quite some time. Consequently this leads to attempts to get additional performance by other means. And the developments in the market clearly indicate that high-end users are willing to consider the adaptation of codes.

To utilize available transistors CPUs with more complex functionality are designed, utilizing SIMD-instructions or providing more operations per cycle than just an add and a multiply. SIMD is "Single Instruction Multiple Data", and it is an idea with quite a history, "Thinking Machines" was founded in the 80s. At Intel the SIMD-instructions initially provided two results in 64-bit-precision per cycle rather than one, in the meantime with AVX it is even four, on recently with AVX512 already eight.

This is still a moderate level of parallelism, but it makes a lot of sense. The electricity consumed by the "administration" of the operations, code fetch and decode, configuration of datapaths on the CPU etc. is a significant portion of the power consumption. If the energy is used not only for one mathematical operation but for two, four, or even eight, the energy per operation is obviously reduced.

In essence, and in order to overcome the performance bottleneck, the architectures developed into the direction which to a larger extent was already realized in the vector supercomputers decades ago! There is almost no architecture left without such features. But SIMD-operations require application codes to be vectorized. During the days of purely scalar computing code developments and programming paradigms did not care for fine-grain data parallelism on scalar CPUs, which is the basis of applicability of SIMD. But now, strictly speaking, there is no scalar CPU left, standard x86-systems do not achieve their optimal performance on purely scalar code as well!

# **Alternative Architectures?**

During recent years GPUs and many-core-architectures are increasingly used in the HPC market. Although these systems are somewhat diverse in detail, in any case the degree of parallelism needed is much higher than in standard CPUs. This points into the same direction, a low-level parallelism is used to address the bottlenecks. In the case of NVIDIA GPUs the individual so-called CUDA-cores, relatively simple entities, are steered by a more complex central processor, realizing a high level of SIMD-parallelism.

So these alternative architectures not only develop into the same direction, the utilization of fine-grain parallelism, they also indicate that coding styles which suite real vector machines will dominate the future software developments. Note that at last some of these systems have an economic backing by mass markets, gaming! But other mass markets are looming, in particular deep learning and data analytics.

# Lessons learned

The standard LINUX-clusters or other systems, which are based on standard technologies, are providing a great tool for science and engineering, and are available to many users. In a lot of cases these systems are sufficient for the job. Consequently NEC has to provide such systems also in the future, and in fact this is a growing business since the late 90s.

In addition, NEC has developed an alternative architecture, the SX-Aurora TSUB-ASA, to tackle the bottlenecks which were described in previous chapters. By the way, TSUBASA is Japanese for "wing".

The business model must be adapted. A system cannot be successful if it is only available in the form of high-end installations. The GPUs and many-coresystems have shown that researchers and students are willing to adapt their projects to a differentiated architecture if it can achieve results, performance or performance per price, which are not possible otherwise.

To make it easy to use and to make the user feel comfortable from the first login the vector-system needs to be closely integrated with what the normal user knows well, specifically a LINUX-based environment.

At the same time NEC must make sure that it will be easy to get a good efficiency from the code porting, it should not be as complicated as CUDA programming, and in fact because of the experience with vector compilers NEC has a great advantage here.

SX-Aurora TSUBASA

# **SX-Aurora TSUBASA** The New Generation NEC Vector Supercomputer

In early 2018 NEC launched the new generation of the SX vector architecture, SX-Aurora TSUBASA, offering a hitherto unparalleled performance especially for memory-bound applications. This is what the new Aurora vector engine is about.

# The SX Vector Architecture from Past to Future

| Туре | Year | Tech-<br>nology | CPU<br>Frequency | CPU<br>Perfor-<br>mance | CPU<br>Memory<br>Bandwidth | Туре              | Year | Tech-<br>nology | CPU<br>Frequency | CPU<br>Perfor-<br>mance    | CPU<br>Memory<br>Bandwidth |

|------|------|-----------------|------------------|-------------------------|----------------------------|-------------------|------|-----------------|------------------|----------------------------|----------------------------|

| SX-2 | 1983 | Bipolar         | 166<br>MHz       | 1.3<br>GFlops           | 10.7<br>GB/sec             | SX-7              | 2002 | 150 nm          | 552<br>MHz       | 8.8<br>GFlops              | 35.3<br>GB/sec             |

| SX-3 | 1989 | Bipolar         | 340<br>MHz       | 5.5<br>GFlops           | 12.8<br>GB/sec             | SX-8              | 2004 | 90 nm           | 1.0<br>GHz       | 16.0<br>GFlops             | 64.0<br>GB/sec             |

| SX-4 | 1994 | 350 nm          | 125<br>Mhz       | 2.0<br>GFlops           | 16.0<br>GB/sec             | 5.9               | 2007 | 65 nm           | 3.2<br>GHz       | 102.4<br>GFlops            | 256.0<br>GB/sec            |

| SX-5 | 1998 | 250 nm          | 250<br>MHz       | 8.0<br>GFlops           | 64.0<br>GB/sec             | SX-ACE            | 2013 | 28 nm           | 1.0<br>GHz       | 256.0<br>GFlops            | 256.0<br>GB/sec            |

| 5X-6 | 2001 | 150 nm          | 500<br>MHz       | 8.0<br>GFlops           | 32.0<br>GB/sec             | SX-Aurora TSUBASA | 2018 | 16 nm           | 1.4-1.6<br>GHz   | 2,150<br>- 2,457<br>GFlops | 1,228.8<br>GB/sec          |

As already stated NEC started marketing the first commercially available generation of this series, the SX-2, in 1983. First systems sold in Europe were SX-3, shared memory machines with up to four very strong processors. The success was continued with the SX-4, with up to 32 strong CPUs on a shared memory, successfully competing against the Cray T90.

With the SX-5 this direction was continued, it was a very successful system pushing the limits of CMOS-based-CPUs and multi-node-configurations. At that time slowly the efforts on the users' side to parallelize their codes using "message passing", mostly PVM and MPI at that time, started to surface, so the need for a huge shared memory system slowly disappeared. Still there were quite some important codes in the market which were only parallel using a shared-memory-paradigm, initially vendor-specific "microtasking" or "autotasking". NEC and some other vendors could automatically parallelize code, and later the standard OpenMP. So there was still sufficient need for a huge and highly capable shared-memory-system.

Because of continued software development more and more codes could utilize distributed memory systems, and moreover the memory architecture of huge shared memory systems became increasingly complex and that way costly. A memory is made of "banks", individual pieces of memory which are used in parallel. In order to provide the data at the necessary speed for a CPU a certain minimum amount of banks per CPU is required, because a bank needs some cycles to recover after every access. Consequently the number of banks had to scale with the number of CPUs, so that the complexity of the network connecting CPUs and banks was growing with the square of the number of CPUs. And if the CPUs became stronger they needed more banks, which made it even worse. So this concept became too expensive.

Already at that time NEC had a lot of experience in mixing MPI- and Open-MP-parallelization in applications, and it turned out that for the very fast CPUs the shared-memory parallelization was typically not really optimal for more than four or eight threads. This number is no basic law of nature, and surely it depends on the individual capability of the CPUs.

NEC adapted the concept accordingly, which lead to the SX-6 and the famous Earth-Simulator, which kept the #1-spot of the Top500 for some years. The Earth-Simulator was a different machine, but based on the same technology level and architecture as the SX-6. These systems were the first implementation ever of a vector CPU on one single chip. The CPU by itself was not the challenge,

SX-Aurora TSUBASA

but the interface to the memory to support the bandwidth needed for this chip, basically the "pins". This kind of packaging technology was always a strong point in NEC's technology portfolio. NEC developed an own interconnect technology, the so-called IXS, a fully non-blocking crossbar. Based on this clusters were built with a log of individual SX-nodes, which by themselves were powerful systems already.

The SX-7 was a somewhat special machine, it was based on the SX-6-technology-level, but featured 32 CPUs on one shared memory.

The SX-8 then was a new implementation again with some advanced features which directly addressed the necessities of certain code structures frequently encountered in applications. The communication between the worldwide organization of application analysts and the hard- and software developers in Japan had proven very fruitful, the SX-8 was very successful in the market.

With the SX-9 the number of CPUs per node was pushed up again to 16 because of certain demands in the market. Just as an indication for the complexity of the memory architecture: the system had 16,384 banks! The peak performance of one node was 1.6 TFlops. Keep in mind that the efficiency achieved on real applications was still in the range of 10% in bad cases, up to 20% or even more, depending on the code. One should not compare this peak performance with some standard chip today, this would be totally misleading.

In November 2014 NEC announced the next generation of the SX-vector product, the SX-ACE. The main design target was the reduction of power consumption per sustained performance, and measurements have proven this has been achieved. In order to do so and in line with the observation that a shared-memory-parallelization with vector CPUs will be useful on four cores, perhaps eight, but normally not beyond that, the individual node consists of a single-chip-four-core-processor, which inherits memory controllers and the interface to the communication interconnect, a next generation of the proprietary IXS. That way a node is a small board, leading to a very compact design. The complicated network between the memory and the CPUs, which took about 70% of the power consumption of an SX-9, was eliminated. And naturally a new generation of LSI and PCB technology leads to a reduction of both power consumption and cost.

The first incarnation of a completely refurbished product line is available now, the NEC SX-Aurora TSUBASA. At times of stagnating core performance of standard components, the NEC system is a clear alternative for quite some application fields.

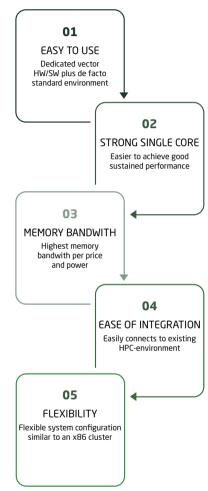

### Aspects to address, lessons learned

NEC has learned the lessons from the past, and the new product addresses these quite distinctively:

- The architecture of the SX-line was developed in the late 1970s, early 1980s. Imagine that at the times of SX-2 a simple add pipe filled a complete rack. The LSI technology today obviously allows for a much higher level of integration, which makes it possible to adapt the architecture to become much more complex. NEC make use of these advantages. The machine features a vector architecture, conceptually very similar to the former SX-line, but with a lot of enhancements.

- → The SX was using big endian. When it was first implemented this was o.k., there were even proprietary formats (Cray, IBM, VAX), and for IEEE it was by no means clear whether little or big endian was going to dominate. Nowadays it is very clear because of the dominance of x86, and one has to assume big endian will disappear. So the new vector system of NEC features little endian, which makes a tight integration into surrounding environments consisting of x86 or ARM much simpler.

- The SX-line was controlled by SUPER-UX, a proprietary UNIX. As much as this was appropriate in the past to provide a stable production quality environment, today Linux is the de facto standard. Users do not want to cope with other UNIX-breeds any more, and they are used to the tools that are available even on the laptop. So for the user to accept a new system we provide a well-familiar Linux environment, and the quasi-standard tools.

- Since many years NEC is enhancing the level of integration of SX-machines into the surrounding environment. The first steps taken already years ago were the provision of a fast parallel shared filesystem to both vector and scalar nodes and the availability of a highly advanced workload manager which could handle even workflows, sequences of jobs with logical dependency, on these different components. The natural extension is the provision of an MPI which can utilize both vector and scalar nodes in one application, for example for coupled models in climatology. NEC is pushing this kind of integration to much higher levels now for a coarse granular hybrid system.

- → Traditionally NEC has always been very successful in quite some vertical markets, namely high-end university sites, in automotive and aerospace, and in meteorology and climatology. And in addition, NEC now explores new vertical markets, as vector processing continues to be the optimal target architecture for many emerging application fields as well. For example in "deep learning" quite some algorithms rely on "sparse matrix times vector", a bandwidth-limited kind of operation for which already the current SX-ACE can achieve remarkable performance and, much more important, industry leading power efficiency in terms of GFlops per Watt, as it shows in the HPCG-benchmark. It is fair to assume that quite some basic algorithmic constructs which were well known in HPC since many years will show up in many other fields that were traditionally not addressed by SX.

- → NEC's SX-system targeted high-end computing in the past, fully blown configurations were very expensive, and even small configurations exceeded the available budgets of individual researchers or small institutes. NEC's new product is designed to provide a solution already at a very low price level. Since a lot of code development is originating from smaller institutions or even from individual scientists or engineers, often as a community effort, the SX-systems were not easily available to code developers and therefore not considered a platform to support. So NEC will intensify the contact to code development people of the present and the future, students, researchers and professional coders, providing them with a full-fledged software development environment comprising high-quality compilers and libraries.

#### NEC addresses all these aspects with the SX-Aurora TSUBASA.

# **Basic Product Strategy**

It is easy to deduct the necessary features of the refurbished product line from the lessons learned in the past combined with the opportunities resulting from the advanced chip design technologies, summarized in one viewgraph:

#### Ease of Use

The user works in a complete Linux environment. There is nothing specific except compilers and highly tuned libraries. An execution can be started on the Linux system either interactively or via a batch system. In principle everything that would compile for a Linux system also compiles for the vector system. The compilers support Fortran 2003, some extensions of Fortran 2008, and C++14. The compilers are able to vectorize and auto-parallelize loops. We support Open-MP and MPI for manual parallelization. With 30 years of experience with vector compilers NEC certainly knows how to do that.

#### **Superior Single Core Performance**

As already emphasized, memory bandwidth is the key ingredient to providing a strong core for real application performance. Low computational efficiency because of lacking access to memory is a waste of energy.

But the current trend in the HPC arena, increasing numbers of cores keeping or even reducing the clock frequency, will not solve this problem. After years of surviving on the progress of higher chip integration, now is the time for an evolution of hardware architectures to achieve higher computational efficiency beyond just a few percent. NEC contributes to this and leads the market of vector supercomputing, achieving high efficiency computing.

The vector-architecture does not only address memory bandwidth, it is also a means coping with ever increasing latencies, in particular the latency of memory access. Latency hiding will be a dominating topic in the future, and a vector architecture is a natural way to address it.

#### Superior Memory Bandwidth

Memory bandwidth is and always has been a hot topic in the HPC market. At all times everybody was aware of the fact that the balance between computational power of a core and available memory bandwidth for this core is of high importance, and in the course of time this balance became worse. NEC leads the market

#### **SX-Aurora TSUBASA**

in terms of memory bandwidth per CPU and even more per core, because this is the indispensable prerequisite for good efficiency for real world computational workload.

The new system features the best memory bandwidth, but even more so the best memory bandwidth per price and per power consumption. Consequently the system achieves very good efficiency with low power consumption.

#### System Integration

Installations will be modular in the future, they will consist of connected clusters with different node architectures. There will be x86-based systems, dual- or more sockets, systems with additional accelerators and GPGPUs, strongly connected systems for "scale-up" and weakly connected for throughput workload.

#### Flexibility

The latest product line of vector systems allows for very flexible configurations, from a deskside system up to a very dense high-end configuration. In particular, it can be configured as a coarse granular hybrid system, a mixture of purely scalar nodes and nodes, which contain vector CPUs, which we call "vector engines" (VE). That way the system can be tailored to every need depending on the nature of the applications and the workload to be processed.

This all implies that a new system needs to fully adapt to all kinds of surroundings, be compatible as much as possible and provide a user environment that people find even on their laptop or deskside x86-workstation.

#### NEC's new product is designed to fulfill this requirement.

# **Hybrid Computing**

Most installations nowadays consist of standard Linux clusters, x86-based systems with an interconnect, mostly InfiniBand, using some standard Linux distribution. These systems serve very well a huge number of scientists and engineers, and depending on the configuration mostly provide the scalability to also tackle challenging scientific problems.

So clearly these systems represent the "standard" for most users. And they represent the basis for the first experiences of most students, and thus for the future of code developments.

In some cases specific requirements show up, and are represented in the requirements of the site, for example:

- → A need for a big SMP-type system with large memory because of a code which is parallelized on shared memory, but not for distributed memory.

- → Some kind of special I/O-features, e.g. for frequent small-block I/O, often for example in chemistry.

- → In rare cases a need for a GPGPU to accelerate special computations.

All these special cases normally lead to minor extensions of an otherwise architecturally homogeneous configuration.

But there are also other cases, and historically these first showed up at some large centers and in the meteo-community. In most cases the workload consists of different types of applications, and the idea is to provide the best or at least a very reasonable platform for each important application.

As one customer from a renowned institute for oceanography once put it: "I want the optimal hardware for each application of interest". In this case there were a handful of applications with quite different characteristics, some matching a scalar architecture, others needed a vector system.

Similarly the need for various systems is easy to understand in case of weatherforecasting: Initially there are tremendous amounts of data from observations from satellites, ships, air planes, weather stations, which need to be assembled and put into some consistent format. In addition such data are archived and partially put into huge databases. Then these data are filtered, preprocessed, sorted, reformatted etc. From there a global weather model is used to calculate long-term and large-scale weather forecast, in most cases on a global scale. Subsequently the output of such forecasts is refined for specified regions, which are of interest to the institution running this system. This leads to "regional forecasts". And in some cases these are further refined, e.g. for very precise short-range forecasts for airports. Then results have to be analyzed, interpreted and visualized. Moreover they are archived together with the initial data.

Clearly this describes a complex workflow, part of which can consist of several tasks running in parallel, with or without human intervention, other parts, especially the weather models, are clearly HPC-type applications, in fact the most demanding ones and historically often the first to use new programming paradigms, because of the numerical challenges.

So in both cases it is understandable that sites will increasingly run different architectures to support the variety of applications. And such strategies have been followed already since the mid-90s by some NEC customers, and still today this is the case.

#### NEC's contribution: a total solution offering

NEC has quite some experiences with regard to hybrid configurations since, for example, the DKRZ was hosting the biggest scientific database in 2005, used for climate data. This database was provided by NEC, as a "side effect" to an HPC-project, which led to a large vector installation. And this database was strongly integrated into the whole workflow of climate-simulations.

Similarly NEC serviced quite some weather sites in different countries with highly complicated configurations, including 24/7 support for the operations.

#### **Coarse-granular hybrid configurations**

This fact is reflected in the hardware. NEC will provide a Linux-based complete cluster at a competitive price, a variety of filesystem appliances for different application needs, GPGPUs and NVME if needed, plus, and that's the difference, a tightly integrated vector system to tackle the most bandwidth demanding applications. It will even feature "hybrid computing" by the provision of an MPI-implementation for the combined use of scalar and vector nodes in one application.

A simple case of such a hybrid application would consist of a weather forecast application running on the vector nodes with I/O-servers, independent MPI-processes to asynchronously handle the tremendous I/O, running on scalar nodes connected to a fast parallel filesystem.

One could also imagine very challenging cases of hybrid applications distributed over vector and scalar nodes, for example climatology simulations. These normally consist of an ocean-code, a model for the dynamics of the atmosphere, atmospheric chemistry, and some other ingredients like sea ice simulations, models of the soil and much more. All these components are coupled by one of the known couplers, OASIS or PRISM or the like.

Atmospheric dynamics and ocean-code are naturally very bandwidth-limited, these should be handled by the vector architecture, while atmospheric chemistry, consisting of a simulation of reaction kinetics running relatively decoupled on each individual grid point, is mostly coded in a very scalar, but also well scaling way. So these portions could well be handled by a scalar cluster.

Consequently the ideal system to execute such simulations is a combination of both components, vector and scalar nodes.

There are other situations, which could be well handled by a hybrid configuration. For example it would be natural to execute very complex simulations on a vector system while running the visualization necessary to drive a cave would be processed by scalar nodes which get the data via MPI. Or one could think about a coupled simulation of the dynamics of an air foil, perhaps simulated by ABAQUS, coupled with a compressible airflow simulation running on a vector.

So in conclusion it starts by providing the best hardware for each type of application in a throughput environment, hybrid workload, over a workchain of applications which represent a production process, and for which individual steps of the process logically depend on each other in some defined way, a hybrid workflow, up to the challenging simulations consisting of coupled components.

# **The Future**

The time is now for some breakthrough in the HPC-market. NEC's legacy in vector computing has been successful in the past, but then again the technological issues that all architectures are facing today are addressed by a vector architecture in a natural way.

And the tight integration of the vector nodes into an otherwise "standard" environment opens a whole new area of supercomputing, namely hybrid applications. This enables the utilization of the most efficient hardware, especially also with regard to energy efficiency, which is the dominant topic in HPC today.

#### NEC - HPC Companion 2019/20 Vector Hardware

# Roadmap

NEC continuously improve the vector architecture in order to provide higher sustained performance. Evolutions of SX-Aurora TSUBASA are shown in this subsection as a first step.

The launch of SX-Aurora TSUBASA was in 2018. This is the first generation of the SX-Aurora TSUBASA series with VE type 10A/10B/10C called a VE10 generation. The processor of the VE10 generation had the world largest memory bandwidth, 1.22TB/s. This high memory bandwidth contributes to provide higher sustained performance especially for memory bandwidth intensive applications.

As an enhanced version of the VE10, NEC introduces a VE10E generation consists of VE Type 10AE/10BE/10CE from beginning of 2020. The new generation pursues higher sustained performance with higher memory bandwidth, 1.35 TB/s per processor.

A VE20 generation is going to appear in 2020 as the successor of the VE10E generation. The memory bandwidth per processor is going to be higher with higher calculation capability.

After the VE20 generation, a VE30 generation having a newly designed vector processor is planned. Through these VE generations, each processor provides the highest level memory bandwidth to accelerate memory bandwidth demanding applications with high power efficiencies. In this section, details of the VE10E generation are described.

# **Vector Architecture**

As stated the SX-Aurora TSUBASA features a vector architecture. So there are vector registers and vector pipes in the first place.

#### **Vector Core**

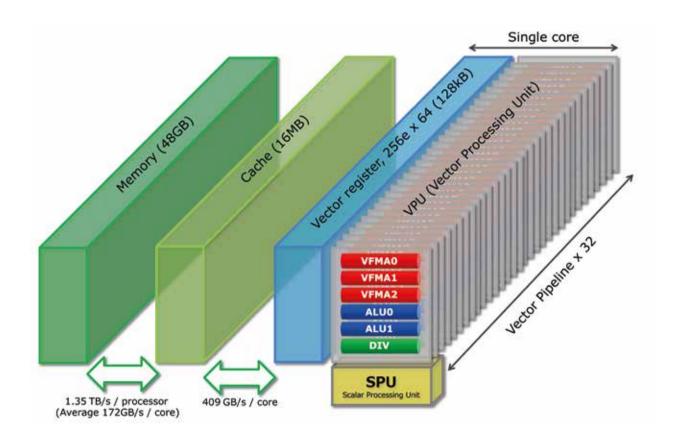

The CPU of SX-Aurora TSUBASA has eight independent vector cores.

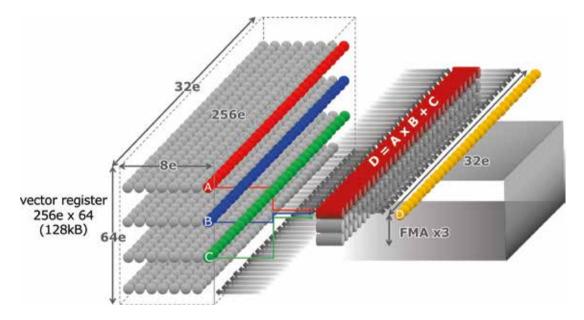

#### **Vector Registers**

There are 64 fully functional vector registers per core, which can feed the functional units or which receive results from those.

This is the first significant and important enhancement compared to the previous SX-systems, which only had eight vector registers, plus 64 so-called vector-data-registers used for keeping intermediate results on the CPU, but lacking the full functionality of a vector register, for example to act as an input to the functional units.

The compiler has a lot more options now to optimize the register usage and consequently this will enhance the efficiency of the system.

The vector registers have 256 entries of 8-Byte-width, thus being able to handle double precision data at full speed. So the full set of registers represents 128 kByte of data readily available for computations at the speed of a register!

#### **Vector Pipes, or Functional Units**

The single core of the SX-Aurora TSUBASA processor has three FMA-units, plus one for divide and sqrt, per core. FMA stands for "Fused Multiply-Add", and reflects an expression like

a \* b + c

The importance of the pipe for divide and sqrt is often underestimated. Indeed such operations are not dominating in normal scientific applications. But once they are needed, they often pop up to be limiting, or at least contribute significantly to the execution time. For example this often happens in the case of molecular dynamics, when distances are important for the calculation of forces between atoms. Other architectures emulate such operations by a software approximation, which can be time consuming.

In order to provide the high computing capability those pipes are inherently a 32-way parallel, means, each FMA unit produces 32 results per cycle.

Traditionally only add- and multiply-operations are counted when computing the peak performance of an architecture. For the system this is then

#### 3 \* 2 \* 32 = 192 floating point operations per cycle

There are more pipes for fixed-point arithmetic and logical operations. And all together they are fully connected to the vector registers by a fully non-blocking crossbar.

A very schematic view on this architecture:

An important enhancement of the system compared to the previous SX-architecture lies in the support of 4-Byte-arithmetic at twice the speed. This means for single precision the system can do 384 floating point operations per cycle. For some application fields, for example crash simulation or seismic imaging, this is considered sufficient precision for certain cases.

# **Core Frequency**

The power-consumption of CPUs is an important problem nowadays, not only for cooling problems, but also for the calculation of the total cost of ownership. Power consumption scales roughly like frequency cubed. At the same time it is inefficient to have a high frequency for the computation while the memory bandwidth, which is dictated by other technologies, cannot deliver sufficient data to justify such a frequency. To achieve such a balance there are two different versions of CPUs with frequencies of

#### 1.4 GHz and 1. 6 GHz

Consequently the single-core performance computations are

#### Double precision: 268.8 GFlops and 307.2 GFlops

#### Single precision: 537.6 GFlops and 614.4 GFlops

To put this into perspective, one core of the system is about as fast as one CPU of the previous product SX-ACE!

# **Scalar Operations**

The scalar portion of the core is not just a scalar CPU, it controls all available resources. The scalar CPU has complete information about all ongoing activities, it can schedule functional units and registers, both vector and scalar registers, and can even reorder operations on several levels to enhance efficiency. This is highly important as it serves to hide latencies, also latencies from memory access, and this was always a big contribution to the efficiency that NEC's vector machines could realize.

This is important to understand, even the best vector code comes with a lot of scalar operations, like updating address registers for vector loads, incrementing and checking loop counters etc. Such operations need to be conducted while the vector pipes are active. But there is plenty of time, or cycles, to complete these operations, which therefore do not affect the performance of the actual computation in the vector pipes.

As a matter of fact already on previous generations of NEC's vector systems optimizing a code caused the hardware counter for "Instructions per second" to decrease, while the counter for "operations per second" was increasing. A vector instruction implies 256 operations in case of an add or a multiply operation for double precision, and once the vector pipes are fully active and no other instructions are necessary any more, instruction issue is reduced. The scientific user needs operations, not instructions.

The scalar portion of the CPU has two level 1 caches for instructions and for operations, each 32 kByte. As an enhancement compared to the previous architecture the system features an additional level 2 cache of 256 kByte, which further enhances the scalar performance and especially decrease the time spent on instruction fetching.

# CPU

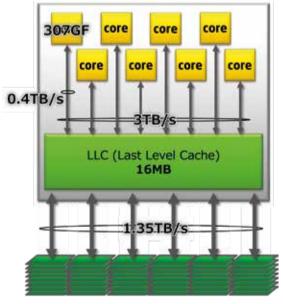

The following figure shows a block diagram of the vector CPU and connected memories.

HBM2 memory x 6

#### Vector Hardware

Before this description, the following sentence should be added.

This CPU mainly consists of eight vector cores and LLC (Last Level Cache) shared by the eight cores.

Because this CPU runs at 1.4 GHz or 1.6 GHz, the CPU performances in double precision and single precision are:

# "Last-Level-Cache" (LLC)

Already with the SX-9 and the SX-ACE NEC introduced the first ever "vector cache", called "Assignable Data Buffer" (ADB) at that time, because it could be software-controlled, data to be cached were "assigned" to reside there. These ADBs were not shared between CPUs or cores.

For the system NEC developed a shared "Last-Level-Cache" (LLC), the first shared vector cache ever. This shared LLC serves all cores together.

The LLC has a "write back" policy, which means data coherency between different cores, LLC and memory is always easily ensured.

At the same time this kind of architecture lends itself easily to a shared memory parallelization, by autoparallelization or OpenMP, while MPI would be used to parallelize over different CPUs.

The last level cache has a line-size of 128 Bytes, and some additional features are implemented to increase the efficiency for strided stores or scatter operations.

# Memory

NEC has investigated the existing memory technologies available for a high-end system, and has chosen to utilize the second generation of the so called "High Bandwidth Memory" standard, HBM2. Such a component is realized by stacking four or eight dies together, and it achieves 230.4 GB/s bandwidth while providing four or eight GBytes of capacity.

Six of these components and the CPU are connected by a so-called "Silicon interposer", a kind of die to mount on and that way connect all pieces as the following picture shows.

NEC uses six such HBM2 components for a total of 24 GByte to 48 GByte per CPU, and 1.35 TB/s bandwidth, which is industry leading, the best bandwidth in the market at this point in time.

#### NEC - HPC Companion 2019/20 Integration

# **Basic concept**

The idea is to take the best of both worlds, the "standard x86-Linux-cluster" and the "high-end vector architecture" and merge this into one product. Combining the favourable features in particular with regard to operating system and user environment the system reflects the basic design strategy sketched earlier.

# Realization

The standard environment is provided by a normal x86 cluster node, it is called "Vector Host" (VH), the vector architecture is added as the so-called "Vector Engine" (VE). These two components are connected by a PCIe Gen.3 x16 interface. The support for forthcoming standards will not pose difficulties.

VE has been realized by PCIe card implementation. One vector CPU, the main memory of the six HBM2 implementation are mainly implemented on the card. A PCIe connector to connect VH is PCIe Gen.3 x16. An actual power consumption of this card is around 250 W, but it strongly depends on each application characteristics executed on the card. A memory bandwidth bound application requires much less power consumption per card because an activation rate of each arithmetic unit becomes lower.

The VE card has three variations called VE1.0 Type 10AE, Type 10BE, and Type 10CE. Type 10AE is a high end specification, and Type 10CE is an entry version.

| VE Type   | frequency<br>(GHz) | core | processor |      |        |      |  |

|-----------|--------------------|------|-----------|------|--------|------|--|

|           |                    | GF   | cores     | DPTF | memory |      |  |

|           |                    |      |           |      | BW     | size |  |

|           |                    |      |           |      | TB/s   | GB   |  |

| Type 10AE | 1.6                | 307  |           | 2.45 | 1.35   | 48   |  |

| Type 10BE | 1.4                | 269  | 8         | 2.15 |        |      |  |

| Type 10CE | 1.4                |      |           |      | 1.22   | 24   |  |

# **Supercomputer with Frontend**

From the type of connection one might be tempted to compare the product with a GPGPU. But it is important to understand,

#### "SX-Aurora TSUBASA is not "yet another accelerator"

The principle of operation is drastically different, in a way the opposite of how typically accelerators work. On NEC's system the complete application runs on the vector CPU, not just parts which are offloaded in some way using paradigms like CUDA or OpenACC or the like.

Rather think of the vector CPU being the major workhorse, the VE, and the x86 node, the VH, being kind of a frontend, which handle compilation or take over typical OS-duties, like resource scheduling, or some specific workloads, or like I/O requests, interactions with filesystems for which the vector CPU is not ideal and much to precious anyway.

The typical usage of accelerators or GPGPUs implies to start on the x86 host and then offload pieces of the workload, like a complete loop nest, to the GPU. This implies to transfer a lot of data back and forth, and in addition this should happen frequently, at the granularity of loop nests, because otherwise the utilization of the GPGPU would be low.

On the NEC system it is the other way round, only those pieces of the application are offloaded to the x86 system which imply activities for which the vector architecture is not ideal, for example I/O requests. In normal applications these should occur less frequently and in addition the amount of data to be transferred should normally be smaller.

# Interconnect

Initially Mellanox InfiniBand EDR and HDR are used.

Note that the vector nodes can communicate with any other vector node in the fabric, and also with any other scalar node, without involvement of the vector host.

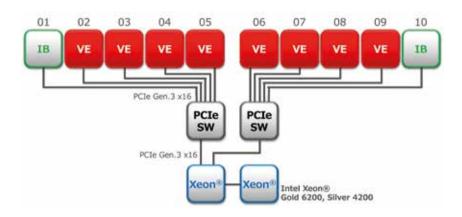

The basic configuration for high-end systems consists of eight VE cards, two Xeon processors, two PCIe switches, and two InfiniBand HCAs as a one server module.

The VEs are connected to the HCAs and to the Xeon CPUs of the VH by the PCIe switches.

MPI-messaging will be implemented by NEC's own MPI, which is "hybrid", means it allows to utilize scalar and VE cores in one application.

Naturally VEs need to exchange information with each other. If they are connected to the same PCIe-switch this kind of messaging is "direct", does not involve the VH except for the initialization mpi\_init.

If the VEs belong to the same VH, but to different PCIe switches, the messages will be routed via the PCIe switches through the PCIe root complex of the Xeon.

Similarly the VEs can exchange data with the VH directly through the PCIe switch, a hybrid utilization.

And moreover the VEs can communicate with other VEs or other scalar cluster-nodes via the IB fabric, which is connected to the PCIe switches.

Overall this concept allows for a very high flexibility both with regard to configurations as well as with regard to its usage.

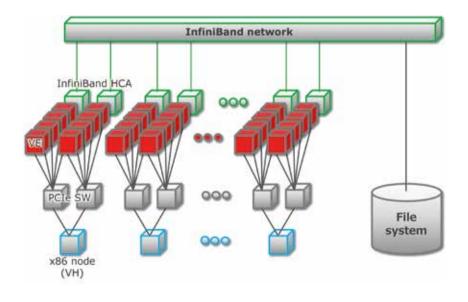

The following figure shows an example of large scale configuration. VE cards are connected with the InfiniBand network as a large scale vector supercomputer.

# **Products of SX-Aurora TSUBASA**

SX-Aurora TSUBASA has mainly three variations of product, A100, A300, and A500 as following figure shows. Such the variety of the product line up can cover wider range of the market or use cases. Each variation of SX-Aurora TSUBASA has each characteristics as following figure shows.

The horizontal-axis shows the cooling mather of each product, which are an air cooling, water cooling door, or a direct liquid cooling (DLC) with water flow. The vertical-axis shows supported VE versions, Type 10AE, Type 10BE, and Type 10CE.

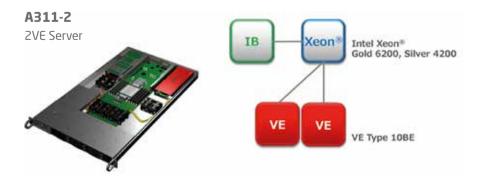

The A100 series is a tower model, which can be used on a desktop. This model is developed to cover kind of personal use for developers and programmers, and mainly consists of one Xeon processor and one VE card of Type 10CE.

**A111-1** 1VE Tower

The A300 series is a standard rack mountable model with air cooling. There are three types of products in this series, A300-2, A300-4, and A300-8. The numbers following A300 are the number of maximum VE cards per each A300 product. Due to the standard rack mount implementation and the air cooling, this series has high configuration flexibility as same as a de-facto standard x86 servers. The supported VE cards are Type 10B and Type 10C.

A block diagram of A100-2 is shown in the following figure. This model consists of one Xeon processor, up to two VE cards, and one IB HCA with 1U implementation.

A300-4 can be implemented up to four VE cards per server. The server mainly consists of two Xeon processors and up to four VE cards of Type 10B or Type 10C. Moreover, up to two IB HCAs can be equipped with this server.

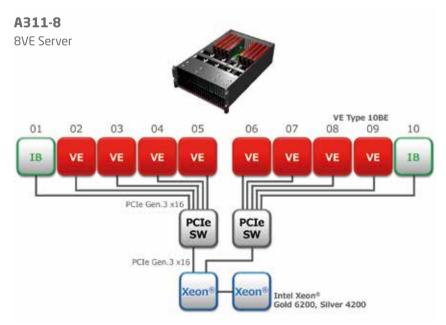

High vector processing power and high memory bandwidth are provided by the A300-8 series. This sever is designed for large scale vector processing by implementing up to eight VE card per two Xeon processors. A big differentiation from A300-2 and A300-4 is that two PCIe switches are located between VE cards and Xeon processors. Due to this implementation, such the eight VE cards can be connected to one Xeon node, and direct MPI communications between VE/VE or VE/IB HCA via a PCIe switch are provided. VE card Type 10B and Type 10C are also supported by this product.

46

The high end product of SX-Aurora TSUBASA is A500-64. Up to 64 VE cards are implemented into one dedicated DLC rack.

Basically, the server unit of A300-8 is used with implementing DLC units and optimizing full rack cooling for a large scale supercomputer operation. Eight servers are implemented into the rack. The high end VE card of Type 10AE is only supported by this DLC supercomputer. The Type 10B VE card is also supported. In order to reduce cooling cost, an inlet water temperature to cool this rack is allowed up to 40 degrees °C called a hot water cooling.

Integration

# Coding, a User's Perspective

What does this now mean for a user, what characteristics of an implementation is required to utilize such an architecture?

Since the length of the vector register is 256, loops are strip mined into pieces of this size. Vector instructions only make sense when the loop length is appropriate, not necessarily 256, in principle the vector pipes can be used with any trip count, but a loop-length 8 or 16 would not lead to the desired performance.

From the mathematical formulation of typical scientific, based on a grid, or a huge number of particles, finite elements or volumes, there is always a sufficient amount of data parallelism in codes, just because it results from the underlying characteristics of the problem and how this is expressed mathematically, for example as a partial differential equation. Nature is local, means things can be described by partial differential equations in some way, and thus are inherently parallel and providing the notion of "neighbourhood". The application should be written in such a way that the compiler could clearly identify such underlying structures.

Surprisingly, this mathematical or physical fact is often not reflected in the way the applications are written, sometimes the structure is rather hidden, or at least not well reflected in how the variables are organized in memory.

People often think in a certain way when coding:

I have an element, a grid point, a particle, an equation, whatsoever. What am I going to do with it?

The vector paradigm is simple, and in a way just the opposite:

I have to execute a certain operation. On which elements, grid points, particles, equations, can I apply it simultaneously?

If this is your way of thinking, you will inevitably write vector code.

What does it imply? For example, a grid point does not have a mathematical meaning, the complete grid is the abstraction of space or space time based on which the mathematical problem is formulated. Similarly, a physical field of whatever kind should be considered a mathematical entity, not the individual value of the density as a "variable" living on a grid point.

Consequently, the grid and the fields living on it should be "recognizable" in the data-structures.

There are codes which use a C structure to represent a grid-point and the "variables", density, temperature, whatsoever, and in the worst case these grid points are connected as a linked list. No compiler on earth can identify the hidden data parallelism any more. And in such a case it is close to impossible to ensure cache locality, and to hide the latency of memory accesses. But both code features are necessary to effectively utilize any modern hardware.

Instead, the fields should lead to arrays, living on a grid. This is simple in the case of structured grids, not so simple but feasible on unstructured grids, admittedly difficult in the case of adaptive refinements for enhanced resolution. Admittedly, there are codes, which do not have anything like a grid. But mostly similar ideas can be applied.

It is a known fact since many years, and although initially it was mainly a problem of vector architectures, nowadays it is more general because of the need for data parallelism to utilize SIMD instructions: in C one should organize variables as a structure of arrays, not as an array of structures. Similarly, more modern: the grid and the mathematical fields should be objects, not the combination of grid point, which is a collection of coordinates, plus the variables on it.

It is basically also this understanding which some years ago lead to the idea of "domain specific languages" (DLC), namely to define a tool to describe an action to be applied to a whole field, for example the application of a differential operator. In the ideal case vendors would provide the means to translate these constructs somehow into machine code in an optimal way for a given architecture. In any case and obviously, this direction exactly represents the vector paradigm.

**NEC HPC Platform for Deep Learning**

# NEC HPC Platform for Deep Learning

The last few years have seen a growing interest in Deep Learning techniques, thanks to the major breakthroughs achieved in the fields of computer vision and natural language processing. Complex problems, such as object detection, text translation and speech recognition, can now be solved with relatively small effort leveraging Deep Learning techniques.

These successes have encouraged researchers to explore many areas of application for such techniques. For example, even large computation tasks generally belonging to the high-performance computing domain, such as fluid mechanics, biology and astrophysics, may benefit from the application of Deep Learning to improve quality of simulations and increase computation performance.

## A Brief Introduction to Deep Learning

At the core of Deep Learning there is a set of algorithms generally called artificial neural networks. An artificial neural network is composed by a set of atomic units, called neurons, which perform very simple computations. When properly combined together, the simple computations of the neurons are able to implement much more complex functions, e.g., to describe the content of an image. The combination of the different neurons is performed using an automated training process, which leverages the *backpropagation* algorithm. When provided with data, the combined computation performed by the neurons is learned via backpropagation by adjusting weights values associated with each neuron, thereby making a neuron relatively more or less important for the target mathematical function. Generally, a neural network requires a big amount of data to be trained, and the more data is provided to the training process, the closer to the target function is the neural network's learned function.

Usually, neurons are grouped together in layers that perform different conceptual operations, depending on the neurons' types and their interconnections. These layers are used as basic building blocks for neural network architectures and, as such, a neural network is generally described as a sequence of layers. There are three main broad types of neural network *architectures* that have been widely used in the last few years:

- Multilayer perceptron (MLP)

- Convolutional neural networks (CNN)

- Recurrent neural networks (RNN)

While these neural network architectures share many common types of layers, they generally provide better results for different specific tasks. For instance, MLP are a good fit to perform tasks on tabular data, convolutional neural networks (CNN) are capable of dealing with data that show some spatial correlation, such as images, and recurrent neural networks are generally well-suited to work with time series.

# **Example Applications**

While use cases such as image recognition are already a quite known field of application for neural networks, there are many other newer fields where this machine learning tool has recently provided interesting results. For instance, NEC is exploring the application of deep learning to several digital health applications, which we briefly describe next.

**Digital pathology.** Pathologists aim to diagnose a patient's current health status as well as forecast how the patient's status is likely to progress in the future. High-resolution images of cells and tissues from sophisticated microscopes are one of their most important tools. Robust detection, segmentation, and classification of tumor, normal tissue, and respective cells are an integral challenge for diagnosis and prognosis from pathology stains. At NEC, we have developed novel CNN architectures to solve problems like characterizing tumor morphology and counting immune cells as diagnostic and prognostic biomarkers.

**Immuno-oncology.** Immunotherapy is a promising therapeutic approach for combating cancer by teaching the patient's own immune system to recognize and destroy cancerous cells. However, each patient is unique, and precision medicine approaches are needed to give each patient the best chance for a positive outcome. We are using novel graph neural networks (a particular sub-family of CNNs) and RNNs to improve the efficacy of these treatments by confronting challenges like genomic characterization of cell subpopulations, prediction

of adverse events following checkpoint inhibitor treatment, and selection of neoantigens as vaccine targets. This technology has been approved by the FDA and EMA for use in clinical trials in the US and Europe.

**Electronic health records.** Modern hospital information systems keep very detailed patient records. The records include many data modalities, including patient demographics, lab measurements, notes from physicians and nurses, movement data during hospital visits, and more. We are applying graph neural networks to extract valuable patterns from these records including outbreaks of dangerous pathogens like Candida auris or methicillin-resistant Staphylococcus aureus (MRSA) within hospitals and prognostic risk indicators for both short-and long-term patient outcomes.

**Drug discovery and repurposing.** Pharmaceutical research aims to discover high-quality drugs which are effective, safe, and cost efficient. Many diverse factors affect these qualities, such as the chemical properties of the drug, how it interacts with a disease on the molecular level, and the genetic background of selected patient cohorts. We represent these myriad properties using a biomedical knowledge graph and use graph neural networks to identify novel relationships like side effects from untested drug combinations and genes affected by diseases. These relationships increase the likelihood that drugs selected for further investigation have a high chance of success; further, the discovered relationships uncover opportunities to repurpose existing drugs for new diseases.

#### Software for Deep Learning

The quick evolution of Deep Learning has been propelled by the availability of a number of software frameworks that simplify the development of neural network algorithms. NEC has been a pioneer in developing such frameworks, contributing to one of the first instances of such software: Torch. Currently, a number of alternatives have emerged, with PyTorch, TensorFlow, MXNet, CNTK being among the most popular deep learning frameworks.

Conceptually, these frameworks provide a ready to use set of neural network building blocks, and a high-level API to implement the neural network layers. Writing a new neural network is as simple as sticking together a few lines of code using the python programming language. For instance, a common code snippet could look like the following:

```

import framework

model = framework.ModelZoo.init("MyNeuralNetwork", ...)

input = (...load input...)

result = model(input)

```

The frameworks will then take care of all the operations required to enable the training of the neural network and its execution.

Under the hood, each of these frameworks maps the high-level API to low-level optimized hardware specific computation libraries. For example, the cuDNN library is used with NVIDIA GPUs that use the CUDA computation model. Given the high-level API, the user of the framework can ignore the low-level hardware details, focusing on the neural network algorithm design. This also provides hardware agnostic implementation of the neural network, since the hardware executor, e.g., a CPU or a GPU, is managed by the framework transparently.

However, the high-level API abstractions may also affect the overall efficiency of the implemented low-level computations. For instance, the high-level APIs generally expose neural network layers as atomic components of a neural network, requiring their execution to happen serially on the underlying hardware. In some cases, the execution of different layers could be instead merged together from a computational perspective, optimizing the use of the underlying hardware, e.g., avoiding the data transfer that usually happens when starting and finishing the computation of a layer.

# **NEC Deep Learning Platform**

Building on its large experience in both AI applications and platforms, NEC designed a next generation deep learning platform aiming at portability, extendibility, usability and efficiency. The NEC's deep learning platform (DLP) seamlessly integrates into popular frameworks, rather than introducing "yet another API". As such, in contrast to other techniques, it does not replace any of the original functionality of the original deep learning frameworks but complements them.

Users continue writing neural networks using their favorite frameworks, e.g., TensorFlow or PyTorch. The NEC platform seamlessly analyzes the neural network descriptions to provide additional hardware compatibility and improve performance.

The NEC DLP reads the description of a neural network defined in the framework's syntax, analyses its structure, and automatically derives a set of optimized computations for the specific neural network the user has described. Then, in addition to the low-level computation functions available in libraries such as NVIDIA cuDNN or Intel MKL-DNN, the NEC platform also generates any additional low-level computation function that may be required by the optimized neural network, for a target hardware executor. This step leverages the expertise of NEC in automated code generation techniques, allowing the system to create on the fly a computation library that is optimized specifically for the user's neural network. The generated code is compiled in implementations that are fully functionally equivalent for the user, which can perform the exact same set of computations on the data, but more efficiently.

A code snippet that uses the NEC DLP looks as follows:

```

import framework

import necdlp.framework as dlp

model = framework.ModelZoo.init("MyNeuralNetwork", ...)

model = dlp.optimize(model)

input = (...load input...)

result = model(input)

```

Two lines of code are added to the previous example to load the NEC DLP and to apply its optimizations to the neural network model.

#### **NEC HPC Platform for Deep Learning**

NEC - HPC Companion 2019/20

| TensorFlow Interface |                           | PyTorch Interface |                 | MxNet Interface     |            | CNTK Interface |                  |  |  |  |  |  |  |

|----------------------|---------------------------|-------------------|-----------------|---------------------|------------|----------------|------------------|--|--|--|--|--|--|

| DLP Interface        |                           |                   |                 |                     |            |                |                  |  |  |  |  |  |  |

| Runtime              |                           |                   |                 |                     | Compiler   |                |                  |  |  |  |  |  |  |

| Framework Runtimes   | TensorFlow                | CUDA              | S               | ers                 | TensorFlow | CUDA           | Device Compilers |  |  |  |  |  |  |

|                      | PyTorch                   | X86               | untime          | Compil              | PyTorch    | X86            |                  |  |  |  |  |  |  |

|                      | MxNet                     | NEC SX-Aurora     | Device Runtimes | Framework Compilers | MxNet      | NEC SX-Aurora  |                  |  |  |  |  |  |  |

|                      | CNTK                      | ARM NEON          |                 | Fran                | CNTK       | ARM NEON       |                  |  |  |  |  |  |  |

| NEC De               | ep Learning Platform Arcl | Opt module        | Optimizers      |                     |            |                |                  |  |  |  |  |  |  |

|                      |                           | Opt module        |                 |                     |            |                |                  |  |  |  |  |  |  |

From an architectural perspective, NEC DLP is shown in the figure above. The rest of this section provides more details on the different architectural parts and on the supported features.

# **Optimization techniques**

Deep Learning frameworks, like TensorFlow and PyTorch, execute their neural networks on a layer-by-layer basis, which can result in an inefficient use of the hardware executor's memory hierarchy and thereby in long execution times. NEC DLP addresses the problem by generating a new custom computation graph customized for the neural network at hand. The NEC platform: 1) analyzes the neural network structure to extract its computation graph; 2) then it performs transformations on this graph to generate more efficient computations taking into account the structure of the graph itself; 3) finally it generates computation libraries that are specific to the newly designed computation graph and to the target hardware. NEC DLP comes with a large set of optimization patterns that can modify the network's structure, improve the reuse of data buffers, optimize the use of the device's memory hierarchy and computation units.

### Software compatibility

The speed at which deep learning architectures are developed, tested, and open-sourced is staggering. For instance, almost every other week a pre-trained model for natural language processing is published (such as ELMO, BERT, XLNet) and shown to be superior to previous ones on established benchmarks. In many cases, these models are written in one specific deep learning framework, optimized for efficiency, and pre-trained on very large datasets. To allow businesses to utilize these models is straight-forward if the deep learning framework matches that of the existing development environment. In many cases, however, there is a mismatch and it is time consuming and expensive to port new architectures and layers to another framework. It is time consuming because the implementations are highly optimized and, therefore, non-trivial to port to other deep learning frameworks. It is expensive because pre-training a model often takes several days on specialized hardware.

NEC DLP, working as a middle layer between specialized hardware and deep learning frameworks, allows one to design and experiment with deep learning models with cross-framework layers. For instance, we can use NEC DLP in Tensorflow to include PyTorch layers and vice versa.

For example, TensorFlow does not support the ConstantPadding layer, which is supported in PyTorch instead. With NEC DLP, the user can use "dlp.nn.padding( type=dlp.PaddingType.Constant, value=N)" to use these layers across frameworks. As the dlp.nn API is identical in all frameworks, a model can also be written entirely in this API and be directly interchanged between the frameworks.

# Hardware support

Another important issue in Deep Learning frameworks is hardware support. Beside the support for Intel CPUs and NVIDIA GPUs, the framework users have to completely rely on the efforts of a vendor to introduce support for their hardware in these frameworks. In PyTorch, over 60,000 lines of code are solely dedicated to NVIDIA GPUs, which gives an idea of the effort required to add support for a new device. Even when a vendor supports a framework, their code updates and changes usually do not get included in the official releases of the frameworks frequently, with hardware related code updates being subject to long delays. This translates into outdated framework variants, vendor specific

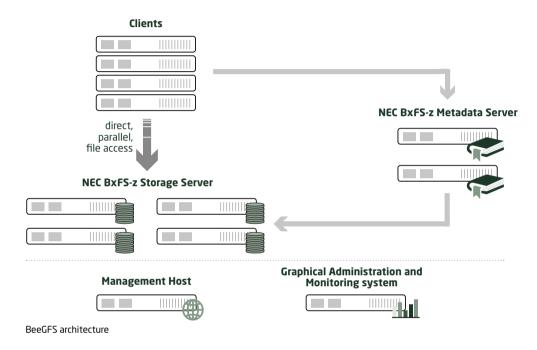

branches with certain limitations, and difficult building procedures. Ultimately, this situation creates significant management complexity and limits the ability of users to take advantage of the most recent hardware and frameworks features.